Intel 22nm工艺3-D结构晶体管技术揭秘

进化之路:32nm平面晶体管 Vs. 3-D晶体管

让我们先从结构的进化上来看看3-D晶体管的发展之路。

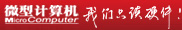

图6

首先让我们来看看教科书上所能学到的晶体管结构。图6是一个标准的晶体管结构,包括源极、漏极以及控制电流的栅极。在正常情况下,由栅极控制晶体管的“开”与“关”两种状态,利用“开”状态下的电子从源极到漏极的流动产生电流。显然,在晶体管处于工作状态的“开”时,我们希望电流量尽可能地大、开关频率更高以获得更强的性能。而在关状态时,我们则希望反型层(电子的流通渠道)上完全没有电子残留,以达到绝对省电的状态。如果在关的过程中产生了电子残留,不但会产生额外的能耗,而且对整个晶体管的电学性能也有较大影响,这就是我们俗称的晶体管电流泄漏(漏电)。在漏电的状况下,很难精确控制晶体管的工作状态。

晶体管的漏电无法绝对避免,而整个业界为解决漏电的问题也进行着各种技术上的尝试。

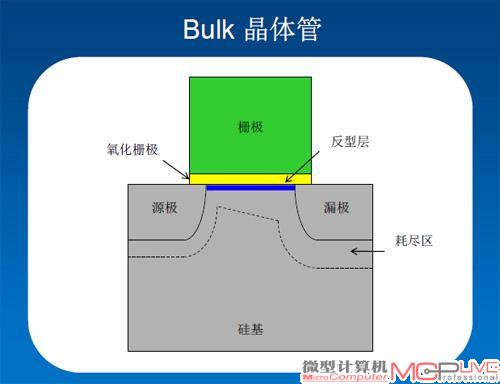

图7 部分耗尽SOI结构

在如何应对漏电的解决方案上,常见的有两种方案,一种就是图7所示的PDSOI(Partly Depleted Silicon-On-Insulator,部分耗尽SOI)结构。由一层氧化物将顶层硅与基层硅隔绝开。由于氧化物绝缘体的存在,来自背面的漏电影响会有一定减少。但由于这种厚膜结构导致浮体物的存在,同样会影响电子在电流沟道中的流通,无法起到极佳的防漏电效果。

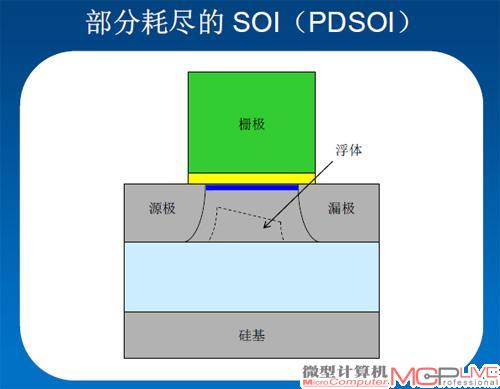

图8

图8显示的则是另一种解决方法,称为FDSOI(Fully Depleted Silicon-On-Insulator)。这种结构将源/漏极部分做得很薄,也常被称为薄膜FDSOI。在这种结构下,浮体部分大大减少甚至消失,对电子在沟道中的流通影响变得非常小,是目前应用较多的一种解决方案。

但Intel却没有使用这两种结构中的任何一种,其中一个重要的原因就是制造成本会增加很多,大约会增加10%。而在使用了三维结构之后,晶体管也能达到全耗尽的效果,既利用了以前的研究成果,同时新的晶体管结构只会带来大约2%到3%的成本上升。

回忆一下32nm晶体管的平面结构,电子流都是在平面结构之下传输的,而三维结构与之对比而言,整个反型层就立起来了。如果单从横面来说,3-D晶体管利用的面积看似非常小,但是整个的电流所利用的面积是非常大的。正是由于这种三维结构的影响,在“开”的状态下,可以得到很强的电流。同时它又充分利用了全耗尽的概念,在“关”的状态下,漏电电流也会降到非常低的程度。这样的话,厂商就可以利用这两种特性调整设备,以满足不同的需要。这也就是3-D晶体管相比平面晶体管的大优势所在。

图9