Intel 22nm工艺3-D结构晶体管技术揭秘

45nm与32nm的HKMG技术

在摩尔定律的预示下,处理器晶体管的尺寸每两年便要缩小到原来的一半。到了65nm工艺时,晶体管中的二氧化硅绝缘层已经达到了5个氧原子的厚度极限。再往后规划的45nm工艺时代,随着晶体管尺寸的再次缩减,源极与漏极之间的距离进一步缩减,而此时二氧化硅绝缘层的厚度已经不可能再缩减,如果此时不能解决栅极向下的电流泄漏问题,摩尔定律的语言也许就此会被打破。

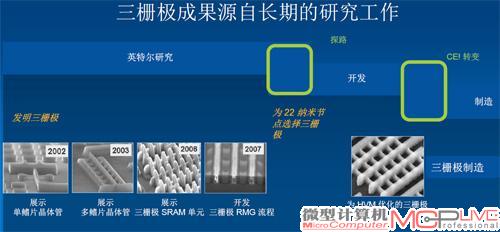

此时,科学家们致力于寻求更新的材料来设计制造晶体管,希望能用高介电常数(Kappa,K)的绝缘材料代替现有的二氧化硅,以提高栅极电容,在不改变电学厚度的同时有效地改善目前看似无法克服的电流泄漏问题。终,元素铪(Hf )以高K值赢得了业界研究人员的信任,HfO2被大量使用在45nm及32nm制作工艺的Intel处理器上,这就是所谓的High-K材料。这种材料在经过超高温的源极/漏极退火处理之后,还可以保持多晶态而且K值还有略微增加的可能,对于降低栅极的电流泄漏有积极的作用,也被一直沿用至今。

Intel的22nm工艺制程研发之路

在使用了High-K材料之后,新的问题又出现了,原来用于制造栅极的多晶硅与新材料兼容性很差,因此必须更换新的栅极材料——用金属电极(Metal Gate)取代多晶硅是一个不错的解决方案。金属电极与高K介质的材料同时使用,因此该工艺也常被称为HKMG。这种组合成功地解决了电子从源极到漏极迁移率降低的问题,可以轻易得到具有高性能的晶体管。

图4

在半导体工艺全面进入45nm乃至32nm之后,HKMG技术几乎被所有的芯片制造厂商所采用,而根据工艺的细分不同又分为前栅极HKMG工艺与后栅极HKMG工艺两大类,分别以IBM和Intel为两大工艺阵营的典型代表。(限于篇幅,本文不对前栅极与后栅极HKMG工艺做详细讲解,有兴趣的读者请自行了解)

解决22nm的困惑,从材质到结构的突破

虽然可以预见,在32nm乃至今后的更先进工艺时代,HKMG技术将在很长一段时间内大行其道,也算是大势所趋。但是,随着制程工艺的进步,在由32nm向22nm迈进的研究过程中,科学家们发现22nm制作工艺的桎梏又出现了——集成度的提升导致晶体管的尺寸进一步缩小,而过小的线宽直接导致了沉积金属栅极材料变得非常困难,甚至无法沉积。

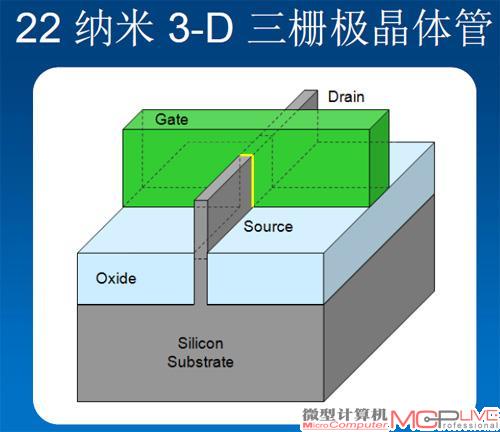

如何解决这个难题?Intel的研究人员想出了一个天马行空却又创意十足的点子——由平面转为三维,由单栅极转为三栅极,这正是Intel提出的22nm工艺中的核心技术——Tri-Gate Transistor(三门晶体管,通常称为三栅极晶体管或3-D晶体管),目前已步入实际生产制造阶段。

图5 Tri-Gate Transistor结构示意图

从图5可以看出,3-D晶体管与之前的晶体管结构相比,大的特别之处就在于将原本是平面的源极、漏极和栅极像鳍状物一样立了起来,形成了立体结构。与32nm平面晶体管相比,可以看出对于栅极而言都是一样的,没有太大变化,不同的是在22nm工艺中,源极与漏极由平面变为了鳍状物的立体结构。而栅极的可利用面积也由一面变为了立体的三面(左侧、右侧与顶面),这就是Intel提出的“3-D Transistor”的名称由来。

看得出来,3-D晶体管其实就是在单个晶体管内集成了三个通道(两个Side Gate和一个Top Gate)。如果将3-D晶体管的正截面剖开,你还可以发现,其实栅极电子束就是一个矩形,矩形除了底面是基板之外,顶端和两侧都是栅电极,好比将32nm的平面晶体管旋转90度之后直接扣在了晶圆的基板之上。