AMD的非对称优势 Fusion APU解析

支持完整乱序执行指令架构

乱序执行指令架构设计理念并不是一种新的技术,这一设计的目的是借助于处理器乱序执行指令的方式来提高性能。在这种结构下,CPU可以更灵活地安排指令,不必因为等待读取内存信息或是特定的执行资源而浪费时间。这种结构有利有弊,好处是处理器的性能得到提升,而代价则是功耗的增加和核心尺寸的增加。因此,为了控制功耗及核心尺寸以满足成本需求,英特尔在针对上网本市场推出的凌动处理器上又回归到以前的顺序执行指令方式,这也是凌动能够实现超低能耗的秘诀。之前威盛在C3系列到C7系列处理器中也使用类似技术。但这种设计让程序指令只能严格按照既有顺序运行,无法充分发挥硬件资源的效率,从而导致性能低下——凌动处理器的性能差强人意。这就给AMD有了可乘之机!

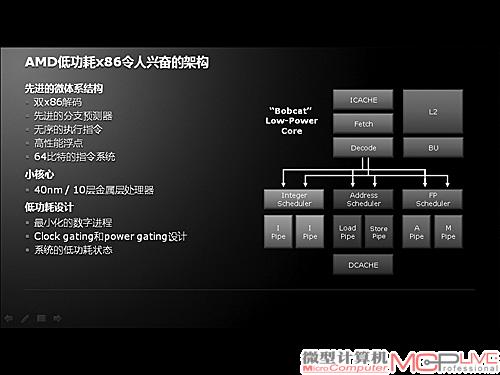

AMD的APU仍将采用完整乱序执行指令架构,集成了两个解码器,同时只能解码两条指令。虽然这比同一时钟周期K8/K10的3指令执行能力以及Bulldozer的4指令执行能力精简不少,但与采用顺序执行设计的凌动相比,Bobcat仍然可以在指令效能方面占据不少优势。

全新C6节能更省电

从技术本身来说,APU是AMD的一次技术革新——通过整合的单芯片,能够完成以往GPU和CPU双芯片才能完成的功效外,单芯片设计还将大幅度降低笔记本电脑的内部设计难度,而且能实现更小的能耗和更长的电池续航时间。另一方面,APU还导入了新的C6待机模式。

Bobcat的架构

处理器的运行模式都被统称为C-states,C0代表处理器正常的运行模式,此时处理器的运行效能是100%。在C0以上的各种模式均属于节电模式,节能模式级别越高,处理器的电路和信号被关掉的部分也就越多。例如,C1状态的耗电量肯定会高于C2状态,当处理器被唤醒时,它也就又回到了C0模式。在AMD的C6模式中,处理器几乎完全关闭,二级缓存也被清空并关闭,处理器中只有一小部分缓存保持工作以供随时唤醒。当处理器从C6模式被唤醒的时候,所有的内部单元会从这个静态存储单元内读取配置信息。因此当处理器被唤醒时,它以前所作的工作都不会丢失。在C6模式下,Bobcat内核可以在不足1W的功率下维持工作,此时却可以提供正常工作时90%的性能,采用双核设计的Ontario APU的TDP更是只有9W之低。